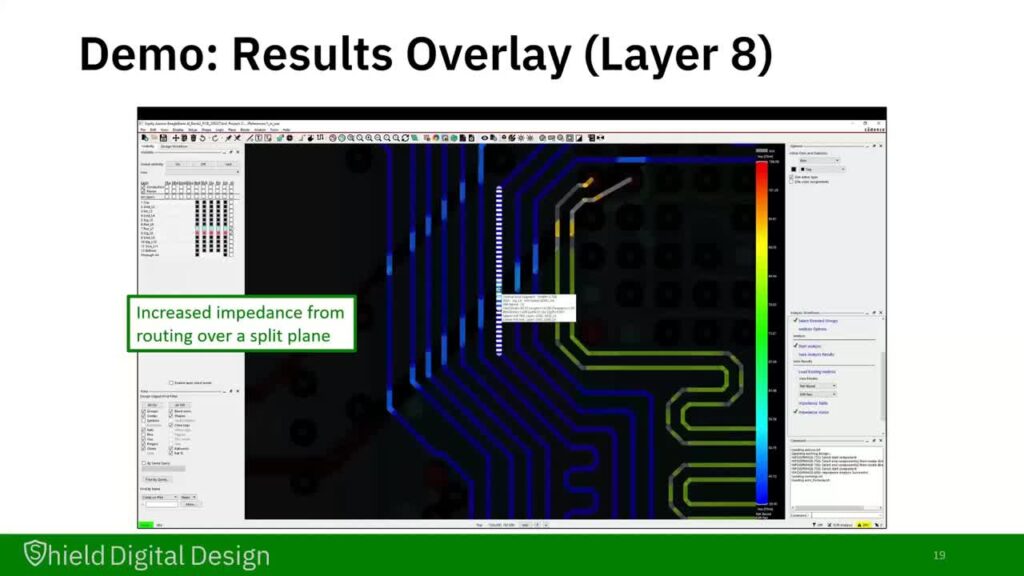

Picture this: you own the design of a fancy new digital PCB with an ultra-fast DDR5 DRAM module to enable some incredible features in your product. Layout has just been completed and you only have a couple of days to finalize your review before signing off with management that it’s ready to go. There was enough time to pass a few signal integrity constraints to the PCB Designer on the interface and your pre-layout simulation gave you a passing report. Unfortunately, when you did a full board extraction of the layout and plugged it into your simulation, the report was showing failures even though the layout looks adequate during visual inspection. With such a short timeline, how are you going to chase down the root cause of the failure in time to ship the board?

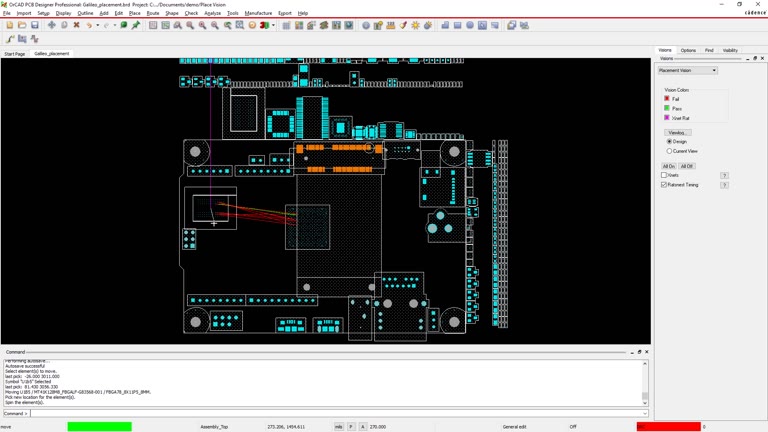

This webinar will provide an example of just that type of situation. It will give the Hardware Engineer, PCB Designer or Signal Integrity Engineer the tools they need to avoid these pitfalls up front as well as the skills to troubleshoot the problems when they do arise. The webinar will be a live demonstration-based presentation with minimal slides and an opportunity for live questions and answers with Sigrity PowerSI certified engineer Stephen Newberry.